Rpi-2040 Development Of a new MiE (micro-ethernet) sync-less two-wire Protocol (Part 1)

In this article the basic concepts of a 'micro-ethernet' is explored and the potential for simultaneous packet signalling across multiple pins.

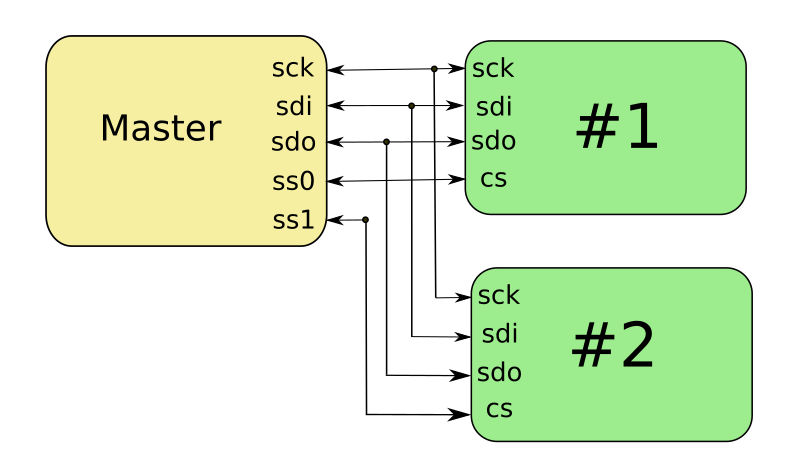

Atypically the RPi2040 chip-set utilizes the SPI communications bus in order to communicate with devices. It can also use UART. A typical SPI wiring diagram would looks as:

- Only one device can communicate to the Master at a time.

- Every device must have a synchronization clock.

- If you had a large number of devices they could wait literally 1000's of bits before their 'turn' to talk on the bus.

- It is good for a small number of devices. After that it is not really usable in a production multi-tasking system.

- PIO submodules can offload CPU clock cycles.

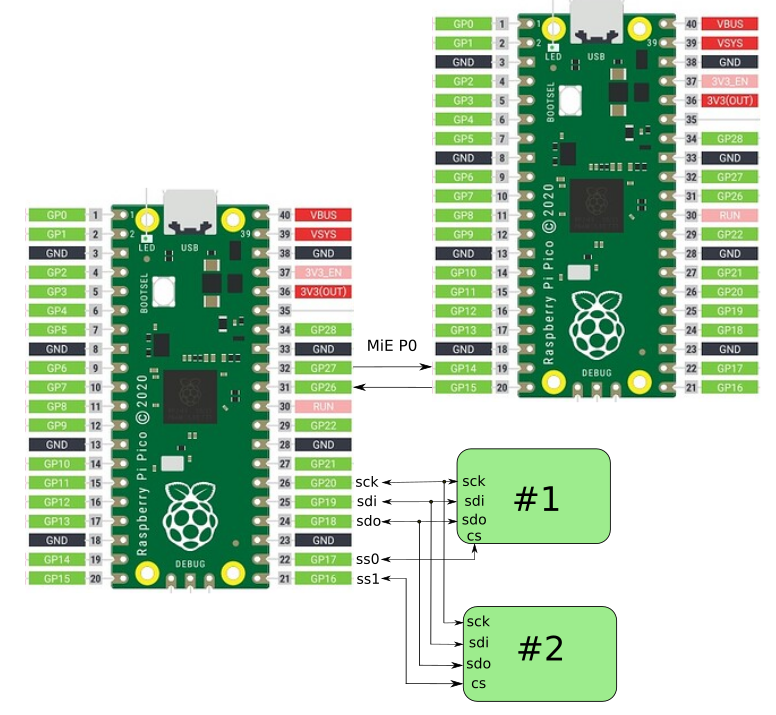

Adding Micro-Ethernet Links to the Raspberry Pi Pico Environment.

- Being able to route packets between Pico's would allow work to be 'offloaded' to sub-devices that can handle SPI bus calls.

- A syncless protocol not requiring any clock is devised. By doing this it removes a significant number of pins for communication between devices.

- The protocol will allow for simultaneous bit receiving/sending across multiple ports.

- Store-And-Forward packeting as in a standard Ethernet Router would be recommended.

- An example diagram:

- MiE P0 would offload SPI device #1 and #2 to the sub-pico which would relay the information up to the 'manager.' This could be extended farther as desired.

- Raspberry Pi Pico's are cheap. At $5 / device it becomes very easy to scale.

- Ring CPU computing becomes available. Backup and fall-back

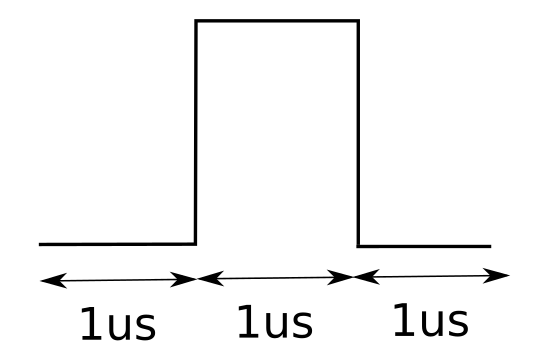

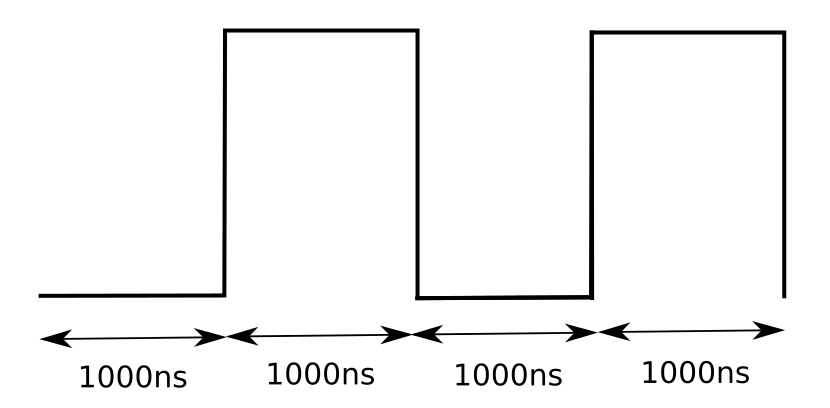

Understanding Variance Timing in Bits

- Normally a bit '1' is the same length as a bit '0'. Consider:

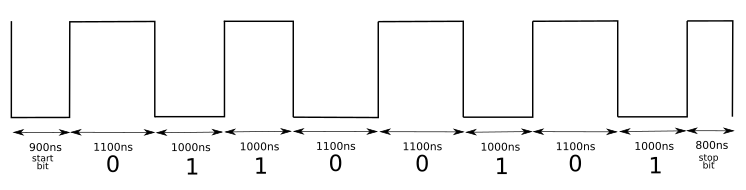

- Instead of uniform bit rates, mathmatically varied bit rates are determined that will define:

- A Stop Bit will be 800 nanoseconds

- A Start Bit will be 900 nanoseconds

- A '1' Bit will be 1000 nanoseconds

- A '0' Bit will be 1100 nanoseconds.

Modified Manchester Coding is developed here thus a '1111' would always have a transistion high-to-low or low-to-high as:

- The high-to-low or low-to-high positions are irrelevant. Only that 1000 ns has expired between transistions.

Now expanding on this for a 8-bit 'packet' would look as:

Bit Precision at 125 Mhz

- At 125 Mhz 8 nanosecond precision is available.

- 800 ns Stop pulse would have a timer value of 100 (0x64) clock cycles.

- 900 ns Start pulse would have a timer value 112.5 (0x71) clock cycles.

- 1000 ns '1' pulse would have a timer value of 125 (0x7D) clock cycles.

- 1100 ns '0' pulse would have a timer value of 137.5 (0x8A) clock cycles.

An example block of code to set / test the TICKINT itself:

- function must be named isr_systick() as:

void isr_systick()

{

printf("Tick fired\n");

systick_hw->csr = 0x7;

systick_hw->rvr = 0x00FFFFFF;

}- Setting a 0x00FFFFFF will trip the interrupt every 0.134 seconds.

Initial setup inside main:

systick_hw->csr = 0x07;

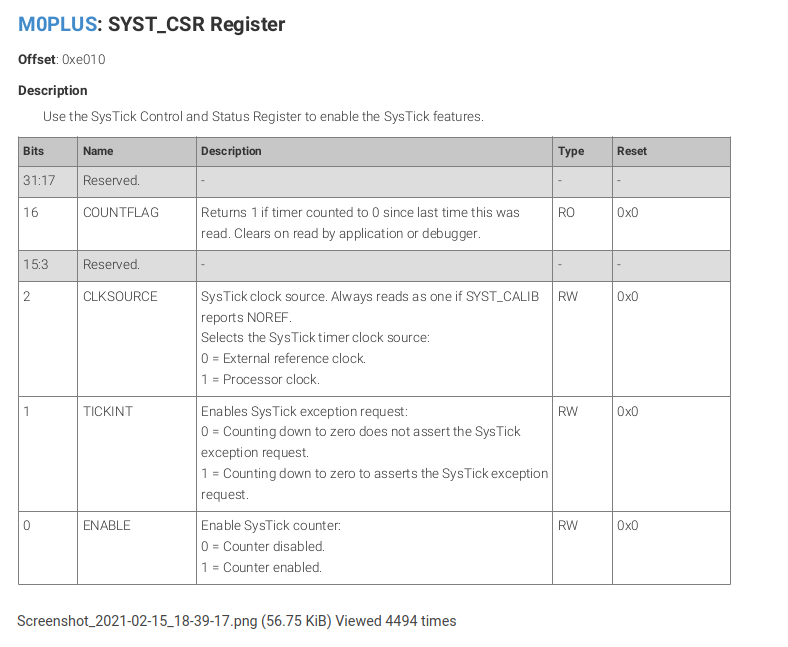

systick_hw->rvr = 0x00FFFFFF;The SYST_CSR Register. When we set:

systick_hw->csr = 0x7;- Bit 2 CLKSOURCE = 1 (Use Processor Clock)

- Bit 1 TICKINT = 1 (Counting Down to 0 asserts Systick interrupt)

- Bit 0 ENABLE = 1 (Counter itself is enabled)

Summary:

- Not only can a standard 'data packet' be defined, by simply reversing the start/stop bit orders a 'control packet' can be defined that can signal back speed control, management, setup channels etc.

- These timing differentials are 'tight.' it may require expansion out to 1500 or 2000 ns as the end goal is not to only signal 1 pin but to potentially signal multple pins in parallel while reading others.

- This may suggest that a pulse width be defined as 1500 x number of active pins.

- Next a protocol definition will be required that will allow for a small addressing space for the 'micro-ethernet protocol, and the concept of multiplex bit encoding of packets from a single clock interrupt source.